1. ņä£ ļĪĀ

ļ░śļÅäņ▓┤ ņé░ņŚģņŚÉņä£ ņø©ņØ┤ĒŹ╝ ļŗ╣ ļööļ░öņØ┤ņŖż ņ╣®ņØś ņłśņ£©ņØä Ļ▓░ņĀĢĒĢśļŖöļŹ░ Ļ░Ćņן ņżæņÜöĒĢ£ ņÜöņØĖļōż ņżæ ĒĢśļéśĻ░Ć ņŖżĒü¼ļØ╝ņØ┤ļĖī ņśüņŚŁņØä ņĄ£ņåīĒÖöĒĢśņŚ¼ ņø©ņØ┤ĒŹ╝ ļŗ╣ ļööļ░öņØ┤ņŖż Ļ░»ņłśļź╝ ĻĘ╣ļīĆĒÖöĒĢśļŖö Ļ▓āņØ┤ļŗż. ņØ┤ļź╝ ņ£äĒĢ┤ ņø©ņØ┤ĒŹ╝ņØś ļŗżņØ┤ņŗ▒ Ļ│ĄņĀĢņŗ£ ļööļ░öņØ┤ņŖżņŚÉ ļ»Ėņ╣śļŖö ņ╣®ĒĢæ ņåÉņāü ļ▓öņ£äļź╝ ņČĢņåīĒĢśļŖö Ļ▓āņØ┤ ļ¦żņÜ░ ņżæņÜöĒĢśļŗż. ĻĖ░ņĪ┤ņØś ļŗżņØ┤ņĢäļ¬¼ļō£ ņ×ģņ×Éļź╝ ļ¦żĻ░£ņ▓┤ļĪ£ĒĢ£ ĻĖ░Ļ│äņĀü ņåīņÜ░ņ×ē Ļ│ĄņĀĢņØś Ļ▓ĮņÜ░ Ļ│ĄņĀĢ ņåŹļÅäĻ░Ć ļ╣Āļź┤Ļ│Ā ļ╣äņÜ®ņØä ņĄ£ņåīĒÖöĒĢĀ ņłś ņ׳ļŗżļŖö ņןņĀÉņØ┤ ņ׳ļŗż. ĻĘĖļ¤¼ļéś 45,000 rpm ņØ┤ņāüņØś ĒÜīņĀäņåŹļÅäļź╝ Ļ░¢ļŖö ļŗżņØ┤ņŗ▒ Ē£ĀĻ│╝ ņø©ņØ┤ĒŹ╝ ņé¼ņØ┤ņØś ĻĖ░Ļ│äņĀüņØĖ ļ¦łņ░░ļĪ£ ņØĖĒĢ┤ ņø©ņØ┤ĒŹ╝ņØś ļČäļ”¼Ļ│╝ņĀĢņŚÉņä£ ĒĢäņŚ░ņĀüņØĖ ĻĖ░Ļ│äņĀüņØĖ ņåÉņāü (ņ”ē, ņ╣®ĒĢæ)ņØ┤ ļ░£ņāØĒĢ£ļŗżļŖö ņ╣śļ¬ģņĀüņØĖ ļŗ©ņĀÉņØ┤ ņ׳ļŗż [1-5]. ļö░ļØ╝ņä£, ĻĖ░Ļ│äņĀü ļŗżņØ┤ņŗ▒ Ļ│ĄņĀĢņ£╝ļĪ£ ļČäļ”¼ļÉśļŖö ļ░śļÅäņ▓┤ ņø©ņØ┤ĒŹ╝ņØś Ļ▓ĮņÜ░ ņ╣®ĒĢæ ņåÉņāüņØä ņłśņÜ®ĒĢĀ ņłś ņ׳ļŖö Ļ│ĄĻ░ä (ņ”ē, ņŖżĒü¼ļØ╝ņØ┤ļĖī ņ¦ĆņŚŁ)ņØ┤ ĒÖĢļ│┤ļÉśņ¢┤ņĢ╝ ĒĢ£ļŗż [5]. ņØ┤ļ¤¼ĒĢ£ Ļ│ĄĻ░äņØĆ ņø©ņØ┤ĒŹ╝ ļŗ╣ ĻĄ┐ļŗżņØ┤ņØś Ļ░»ņłśļź╝ ļŖśļ”¼ļŖöļŹ░ ņןņĢĀņÜöņØĖņØ┤ ļÉ£ļŗż. ĻĘĖļ¤╝ņŚÉļÅä ļČłĻĄ¼ĒĢśĻ│Ā ņĀĆļĀ┤ĒĢ£ Ļ│ĄņĀĢļ╣äņÜ®ņ£╝ļĪ£ ļ╣ĀļźĖ Ļ│ĄņĀĢņåŹļÅäņŚÉ ļīĆĒĢ£ ņןņĀÉņØ┤ ņ׳ņ¢┤ ļæÉĻ║╝ņÜ┤ ņø©ņØ┤ĒŹ╝ļéś ļŗżņĖĄ ņø©ņØ┤ĒŹ╝ņØś ļŗżņØ┤ņŗ▒ņŚÉ ņåīņÜ░ņ×ē Ļ│ĄņĀĢņØ┤ ņĢäņ¦üļÅä ļäÉļ”¼ ĒÖ£ņÜ®ļÉśĻ│Ā ņ׳ļŗż. ļ░śļ®┤, ņø©ņØ┤ĒŹ╝ņØś ļæÉĻ╗śĻ░Ć ņ¢ćņØä Ļ▓ĮņÜ░ ļĀłņØ┤ņĀĆļź╝ ņØ┤ņÜ®ĒĢ£ ļŗżņØ┤ņŗ▒ ļ░®ļ▓ĢņØ┤ ļ│æĒ¢ēĒĢśņŚ¼ ņØ┤ņÜ®ļÉśĻ│Ā ņ׳ļŗż [6-8]. ņ”ē, ļĀłņØ┤ņĀĆņØś ļåÆņØĆ ņŚ┤ņŚÉļäłņ¦Ćļź╝ ņØ┤ņÜ®ĒĢśņŚ¼ ņø©ņØ┤ĒŹ╝ņØś ļČäļ”¼ņäĀņØä ļö░ļØ╝ ņø©ņØ┤ĒŹ╝ļź╝ ļģ╣ņŚ¼ ņø©ņØ┤ĒŹ╝ļź╝ ļČäļ”¼ĒĢśļŖö Ļ│ĄņĀĢņØ┤ļŗż. ņØ┤ļ¤¼ĒĢ£ ļĀłņØ┤ņĀĆ ņ¢┤ļĖīļĀłņØ┤ņģś Ļ│ĄņĀĢņØś Ļ▓ĮņÜ░ ņ╣®ĒĢæņØĆ ņĄ£ņåīĒÖöĒĢĀ ņłś ņ׳ņ£╝ļéś ņø©ņØ┤ĒŹ╝ņØś Ēæ£ļ®┤ņØ┤ ņ¦ĆņåŹņĀüņ£╝ļĪ£ ļĀłņØ┤ņĀĆņØś ļåÆņØĆ ņŚ┤ņŚÉļäłņ¦ĆņŚÉ ļģĖņČ£ļÉśņ¢┤ ĒÜīļĪ£Ļ░Ć ņןņ░®ļÉ£ ļööļ░öņØ┤ņŖżĻ░Ć ņåÉņāüļÉĀ ņłś ņ׳ļŗżļŖö ļŗ©ņĀÉņØ┤ ņ׳ļŗż [6-8]. ņØ┤ņÖĆ Ļ░ÖņØĆ ļŗ©ņĀÉņØä ļ│┤ņÖäĒĢśĻĖ░ ņ£äĒĢ┤ ļ│Ė ņŚ░ĻĄ¼ņŚÉņä£ļŖö ņø©ņØ┤ĒŹ╝ļź╝ ļĀłņØ┤ņĀĆ ņ¢┤ļĖīļĀłņØ┤ņģśņŚÉ ņØśĒĢ┤ ņÖäņĀäĒ׳ ļČäļ”¼ņŗ£Ēéżņ¦Ć ņĢŖĻ│Ā ļīĆņŗĀ ļĀłņØ┤ņĀĆņŚÉ ņØśĒĢ┤ ņø©ņØ┤ĒŹ╝ Ēæ£ļ®┤ņŚÉ ļČäļ”¼ ĒÖłļ¦īņØä ļ¦īļōĀ Ēøä ņø©ņØ┤ĒŹ╝ Ēæ£ļ®┤ņŚÉ ņĀæņ░® ņ×¼ļŻīļź╝ ļČĆņ░®ĒĢ£ Ēøä ņĀüņĀĢĒĢ£ ņś©ļÅäĻ╣īņ¦Ć Ļ░ĆņŚ┤ĒĢśņŚ¼ ņŚ┤ ĒīĮņ░ĮņØä ņ£ĀļÅäĒĢśņŚ¼ ļČäļ”¼ ĒÖłņŚÉņä£ ņø©ņØ┤ĒŹ╝ņØś ļČäļ”¼Ļ░Ć ļ░£ņāØĒĢśļÅäļĪØ ĒĢśļŖö ļŗżņØ┤ņŗ▒ Ļ│ĄņĀĢņØä ņŗ£ĒŚśĒĢśĻ│Āņ×É ĒĢ£ļŗż. ņØ┤ļ¤¼ĒĢ£ Ļ│ĄņĀĢņØĆ ņØ┤ļ»Ė Ļ░£ļ░£ļÉśņŚłņ£╝ļéś ņĄ£ņĀüņØś ļČäļ”¼ ĒÖłņØä ļ¦īļōżĻĖ░ ņ£äĒĢ£ ļĀłņØ┤ņĀĆ Ļ│ĄņĀĢņØś ņĄ£ņĀüĒÖö ļ░®ņĢłņŚÉ ļīĆĒĢ£ ņŚ░ĻĄ¼ļéś ļĀłņØ┤ņĀĆ Ļ│ĄņĀĢļ│ä ļśÉļŖö ĒÖłņØś ļ¬©ņ¢æņŚÉ ļö░ļØ╝ ļČäļ”¼ ņø©ņØ┤ĒŹ╝ņŚÉ ļ░£ņāØĻ░ĆļŖźĒĢ£ ņ╣®ĒĢæņŚÉ ļīĆĒĢ£ ņŚ░ĻĄ¼ļŖö ņāüļŗ╣Ē׳ ļ»Ėņ¦äĒĢ£ ĒÄĖņØ┤ļŗż [5]. ļö░ļØ╝ņä£ ļ│Ė ņŚ░ĻĄ¼ņŚÉņä£ļŖö ņĄ£ņĀüņØś ļČäļ”¼ ĒÖłņØä ļ¦īļōżĻĖ░ ņ£äĒĢ£ ņĄ£ņĀüņØś ļĀłņØ┤ņĀĆ Ļ│ĄņĀĢņĪ░Ļ▒┤ņØä ņ░ŠĻĖ░ ņ£äĒĢ┤ ļĀłņØ┤ņĀĆņØś ņĀäļĀź, ņŖżņ║ö ņåŹļÅä ļ░Å ņŖżņ║ö Ēܤņłś ļō▒ņØä ņ░©ļ│äĒÖöņŚÉ ļö░ļźĖ ņø©ņØ┤ĒŹ╝ ļŗżņØ┤ņŗ▒ņØś ĒÜ©ņ£©ņä▒ņŚÉ ļīĆĒĢ┤ ņ¦æņżæņĀüņ£╝ļĪ£ ņŚ░ĻĄ¼ĒĢśĻ│Āņ×É ĒĢ£ļŗż. ĒŖ╣ļ│äĒ׳, ņŚ¼ļ¤¼ ļĀłņØ┤ņĀĆ Ļ│ĄņĀĢņĪ░Ļ▒┤ņŚÉ ļö░ļØ╝ ņŗżļ”¼ņĮś ņø©ņØ┤ĒŹ╝ ņāüņŚÉ ņ¢┤ļ¢ĀĒĢ£ ļČäļ”¼ ĒÖłņØ┤ ļ░£ņāØļÉĀ ņłś ņ׳ņ£╝ļ®░, ĻĘĖņŚÉļö░ļØ╝ ņø©ņØ┤ĒŹ╝ ņĄ£ņóģ ļČäļ”¼ņŗ£ ņ╣®ĒĢæ ņåÉņāüņØĆ ņ¢┤ļ¢ĀĒĢ£ ņ¢æņāüņ£╝ļĪ£ ņĀäĻ░£ļÉĀ ņłś ņ׳ļŖöņ¦ĆņŚÉ ļīĆĒĢ£ ņŗ¼ļÅäņ׳ļŖö ņŚ░ĻĄ¼Ļ░Ć ņ¦äĒ¢ēļÉĀ ņśłņĀĢņØ┤ļŗż. ĻĘĖ Ļ▓░Ļ│╝ļź╝ ļ░öĒāĢņ£╝ļĪ£ ņø©ņØ┤ĒŹ╝ ļŗ╣ ļööļ░öņØ┤ņŖż ņłśņ£©ņØä ĻĘ╣ļīĆĒÖöĒĢśĻĖ░ ņ£äĒĢ┤ ņĄ£ņĀüņØś ļŗżņØ┤ņŗ▒ Ļ│ĄņĀĢņĪ░Ļ▒┤ņØä ļ¦łļĀ©ĒĢśĻ│Āņ×É ĒĢ£ļŗż.

2. ņŗżĒŚś ļ░®ļ▓Ģ

ļŗżņØ┤ņŗ▒ Ļ│ĄņĀĢņØä ņ£äĒĢ┤ 12ņØĖņ╣ś ņ¦üĻ▓Į ĻĘĖļ”¼Ļ│Ā 50 um ļæÉĻ╗śņØś ņŗżļ”¼ņĮś ļŗ©Ļ▓░ņĀĢ ņø©ņØ┤ĒŹ╝Ļ░Ć ņé¼ņÜ®ļÉśņŚłļŗż. ņø©ņØ┤ĒŹ╝ļōżņŚÉ ņŚ¼ļ¤¼ ĒśĢĒā£ņØś ļČäļ”¼ ĒÖłļōżņØä ĒśĢņä▒ĒĢ£ Ēøä ņø©ņØ┤ĒŹ╝ņŚÉ ņĀæņ░®ņ×¼ļź╝ ļČĆņ░®ĒĢśņŚ¼ ĒĢ┤ļŗ╣ ņø©ņØ┤ĒŹ╝ļōżņØä ļČäļ”¼ĒĢśĻĖ░ņŚÉ ņĀüĒĢ®ĒĢ£ 150 ┬░CĻ╣īņ¦Ć Ļ░ĆņŚ┤ĒĢśņŚ¼ ņø©ņØ┤ĒŹ╝ņØś ļČäļ”¼ ĒÖłņŚÉ ņØĖņןņØæļĀźņØä ņ£ĀļÅäĒĢśņŚ¼ ņø©ņØ┤ĒŹ╝ļź╝ ņĄ£ņóģ ļČäļ”¼ņŗ£ĒéżļŖö Ļ│ĄņĀĢļ░®ļ▓ĢņØ┤ ņ▒äĒāØļÉśņŚłļŗż. ņĀæņ░®ņ×¼ļŖö ņŗżļ”¼ņĮś ņø©ņØ┤ĒŹ╝ņØś ņŚ┤ĒīĮņ░ĮĻ│äņłś (2.3 ├Ś 10-6 /┬░C) ļ│┤ļŗż ņŚ┤ĒīĮņ░ĮĻ│äņłśĻ░Ć 80ļ░░ ņĀĢļÅä Ēü░ ņŗżļ”¼ņĮś Ļ│Āļ¼┤ (C2H802SiņØä ņČĢĒĢ®ņŗ£ņ╝£ ļ¦īļōĀ Ļ│ĀļČäņ×Éņ×¼ļŻī)ļź╝ ņø©ņØ┤ĒŹ╝ņÖĆ ļÅÖņØ╝ĒĢ£ ļæÉĻ╗śļĪ£ ņø©ņØ┤ĒŹ╝ņŚÉ ņĀæņ░®ĒĢśļŖö ļ░®ļ▓ĢņØ┤ ņ▒äĒāØļÉśņŚłļŗż.

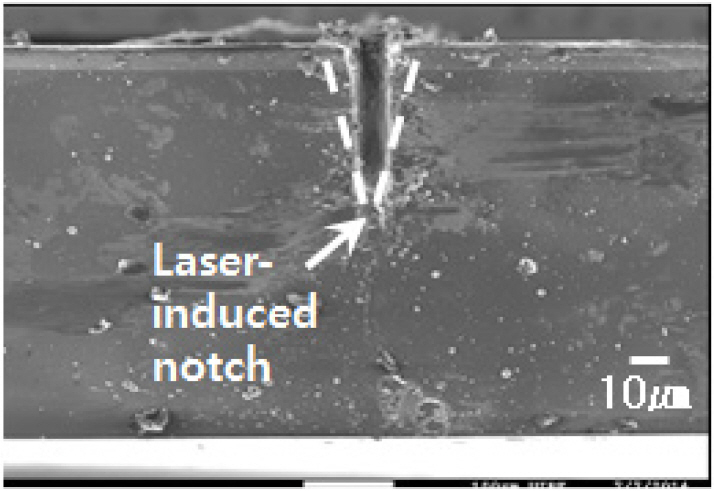

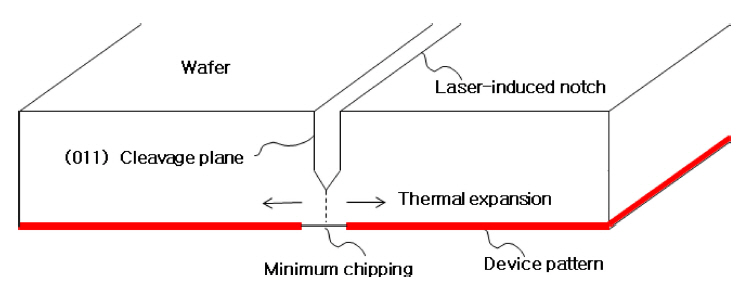

ĻĘĖļ”╝ 1ņØĆ ļ│Ė ņŚ░ĻĄ¼ņŚÉņä£ ĒÖ£ņÜ®ļÉ£ ņø©ņØ┤ĒŹ╝ ļŗżņØ┤ņŗ▒ Ļ│ĄņĀĢņØä ļÅäņŗØņĀüņ£╝ļĪ£ ņäżļ¬ģĒĢ£ ĻĘĖļ”╝ņØ┤ļŗż. ĻĘĖļ”╝ 1ņŚÉņä£ ļ│╝ ņłś ņ׳ļō»ņØ┤ ļööļ░öņØ┤ņŖżĻ░Ć ņןņ░®ļÉĀ ņø©ņØ┤ĒŹ╝ Ēøäļ®┤ņŚÉ ļĀłņØ┤ņĀĆ ļ╣öņØä ņŖżĒü¼ļØ╝ņØ┤ļĖī ņ¦ĆņŚŁ ņżæņĢÖ ļČĆņ£äļź╝ ļö░ļØ╝ ņĪ░ņé¼ĒĢśņŚ¼ ĒĢ┤ļŗ╣ ņ¦ĆņŚŁņŚÉ ĻĘĖļŻ©ļĖīļź╝ ĒśĢņä▒ĒĢ£ Ēøä ņĀæņ░®Ēģīņ×ģņØś ņŚ┤ĒīĮņ░ĮņŚÉ ņØśĒĢ┤ ņø©ņØ┤ĒŹ╝ļź╝ ņĄ£ņóģ ļČäļ”¼ĒĢśļŖö Ļ│ĄņĀĢņØ┤ ņĀüņÜ®ļÉśņŚłļŗż. ļĀłņØ┤ņĀĆ Ļ│ĄņĀĢļ│ä ņø©ņØ┤ĒŹ╝ Ēæ£ļ®┤ņŚÉ ļ░£ņāØĒĢ£ ļČäļ”¼ ĒÖłņØś ļŗ©ļ®┤Ļ│╝ Ēīīļŗ©ļ®┤ ļČäņäØņØä ņ£äĒĢ┤ optical microscope, scanning electron microscope ĻĘĖļ”¼Ļ│Ā atomic force microscopeĻ░Ć ĒÖ£ņÜ®ļÉśņŚłļŗż. ļĀłņØ┤ņĀĆņØś Ļ│ĄņĀĢ ņĪ░Ļ▒┤ļ│ä ņø©ņØ┤ĒŹ╝ņØś ļŗżņØ┤ņŗ▒ ĒÜ©ņ£©ņä▒ ĒÅēĻ░Ćļź╝ ņ£äĒĢ┤ ļĀłņØ┤ņĀĆņØś ņĀäļĀźņØĆ 25~100W ĻĘĖļ”¼Ļ│Ā ņø©ņØ┤ĒŹ╝ņŚÉ ļĀłņØ┤ņĀĆ ļ╣öņØś ņĪ░ņé¼ ņåŹļÅäļŖö 100~700 mm/secļĪ£ ņ░©ļ│äĒÖöĒĢśņśĆļŗż. ļśÉĒĢ£, ņø©ņØ┤ĒŹ╝ ļŗżņØ┤ņŗ▒ņØä ņ£äĒĢ┤ ļĀłņØ┤ņĀĆ ļ╣öņØś ņŖżņ║öņåŹļÅäļź╝ ņĀüņĀĢ ņåŹļÅä ņØ┤ĒĢśļĪ£ ļé«ņČöļŖö Ļ▓āņØĆ ļ░śļÅäņ▓┤ Ļ│ĄņĀĢņŗ£Ļ░äņØä ņ¦ĆņŚ░ņŗ£ņ╝£ ņĀ£ņĪ░ņøÉĻ░ĆņŚÉ ņ¦üņĀæņĀüņØĖ ļČĆļŗ┤ņØä ņżä ņłś ņ׳ļŗżļŖö ņĀÉņØä Ļ│ĀļĀżĒĢśņŚ¼ 25~100WņØś ļĀłņØ┤ņĀĆ ņĀäļĀź ļ▓öņ£äņŚÉņä£ ļĀłņØ┤ņĀĆ ļ╣öņØś ņĪ░ņé¼ņåŹļÅäļź╝ 700 mm/secļĪ£ Ļ│ĀņĀĢĒĢ£ Ēøä ļĀłņØ┤ņĀĆ ļ╣öņØś ņĪ░ņé¼ Ēܤņłśļź╝ 1ĒÜīņŚÉņä£ 7ĒÜīĻ╣īņ¦Ć ņ░©ļ│äĒÖöĒĢśņŚ¼ ļČäļ”¼ ĒÖłņŚÉ ļīĆĒĢ£ ļČäņäØņØ┤ ņ¦äĒ¢ēļÉśņŚłļŗż. ņØ┤Ēøä ņŚ¼ļ¤¼ ļĀłņØ┤ņĀĆ Ļ│ĄņĀĢļ│ä ļČäļ”¼ ĒÖłņØä Ļ░Ćņ¦ä ņø©ņØ┤ĒŹ╝ļōżņØĆ ņĀæņ░® ĒģīņØ┤Ēöäļź╝ ļČĆņ░®ĒĢśņŚ¼ 0 ┬░CĻ╣īņ¦Ć ļāēĻ░üĒĢ£ Ēøä ļŗżņŗ£ 150 ┬░CĻ╣īņ¦Ć Ļ░ĆņŚ┤ĒĢśņŚ¼ ņø©ņØ┤ĒŹ╝ņØś ņĄ£ņóģļČäļ”¼ļź╝ ņ£ĀļÅäĒĢśņśĆļŗż. ļ│Ė ņŚ░ĻĄ¼ņŚÉņä£ ņ▒äĒāØļÉ£ ņś©ļÅäļ▓öņ£äļŖö ļ░śļÅäņ▓┤ ņĀ£ĒÆłņØś ņŗĀļó░ņä▒ ņŚ░ĻĄ¼Ļ│╝ņĀĢņŚÉņä£ ĒĢäņŚ░ņĀüņ£╝ļĪ£ ņĀüņÜ®ļÉśļŖö ņś©ļÅäļ▓öņ£ä ļé┤ņŚÉņä£ ņŗ£Ē¢ēļÉśņ¢┤ ņ░©Ēøä ļ░śļÅäņ▓┤ ĒÜīļĪ£ņØś ņåÉņāüņŚÉ ņĀäĒśĆ ņśüĒ¢źņØä ļ»Ėņ╣śņ¦Ć ņĢŖļŖö ņś©ļÅäļ▓öņ£äņØ┤ļŗż. ļĀłņØ┤ņĀĆ Ļ│ĄņĀĢļ│ä ņø©ņØ┤ĒŹ╝ņŚÉ ļ░£ņāØĒĢśļŖö ņ╣®ĒĢæ ņåÉņāü ļ▓öņ£äļŖö optical microscopeņÖĆ scanning electron microscopeļź╝ ņØ┤ņÜ®ĒĢśņŚ¼ ņĖĪņĀĢļÉśņŚłĻ│Ā, Ļ░Ćņן Ēü░ ņ╣®ĒĢæņåÉņāü ļ▓öņ£äĻ░Ć ļĀłņØ┤ņĀĆ Ļ│ĄņĀĢ ņĪ░Ļ▒┤ņŚÉ ļö░ļØ╝ ļÅäĒæ£ļĪ£ ņ×æņä▒ļÉśņŚłļŗż. ļśÉĒĢ£, Ļ░ü Ļ│ĄņĀĢļ│äļĪ£ ņ░©ļ│äĒÖöļÉśņ¢┤ ļČäļ”¼ļÉ£ ļŗżņØ┤ņŗ▒ ņĀłļŗ©ļ®┤ņØĆ ļČäļ”¼Ļ│╝ņĀĢņŚÉņä£ņØś ļ▓ĮĻ░£ ĒīīĻ┤┤ņÖĆņØś ņŚ░Ļ┤Ćņä▒ Ļ▓Ćņ”ØņØä ņ£äĒĢ┤ AFMņØä ņØ┤ņÜ®ĒĢśņŚ¼ ņĀĢļ░Ć ļČäņäØļÉśņŚłļŗż.

3. Ļ▓░Ļ│╝ ļ░Å Ļ│Āņ░░

ļ│Ė ņŚ░ĻĄ¼ņŚÉņä£ļŖö ĒÜīļĪ£ņŚÉ ņ¦üņĀæņĀüņØĖ ņŚ┤ņåÉņāüņØä ņśłļ░®ĒĢśĻĖ░ ņ£äĒĢ┤ ļĀłņØ┤ņĀĆ ņ¢┤ļĖīļĀłņØ┤ņģś Ļ│ĄņĀĢņØĆ ņø©ņØ┤ĒŹ╝ ņØ┤ļ®┤ņŚÉ ļČäļ”¼ ĒÖłņØä ļ¦īļō£ļŖö ņŚŁĒĢĀņŚÉļ¦ī ĒĢ£ņĀĢļÉ£ļŗż. ĻĘĖļ¤╝ņŚÉļÅä ļČłĻĄ¼ĒĢśĻ│Ā ņŚ┤ĒīĮņ░ĮņŚÉ ņØśĒĢ£ ņø©ņØ┤ĒŹ╝ņØś ņĄ£ņóģņĀüņØĖ ļČäļ”¼ļŖö ņØĖņןņä▒ļČäņØś ņØæļĀźņŚÉ ņØśĒĢ┤ ĻĖ░Ļ│äņĀüņ£╝ļĪ£ ļČäļ”¼ļÉśļŖö Ļ│╝ņĀĢņØä Ļ▓¬Ļ▓ī ļÉśņ¢┤ ļČäļ”¼ļÉ£ ļŗżņØ┤ņŚÉ ļ»ĖņäĖĒĢ£ ņ╣®ĒĢæ ņåÉņāüņØ┤ ļ░£ņāØĒĢĀ ņłś ņ׳ļŗż. ĻĘĖļ”╝ 2ļŖö ļĀłņØ┤ņĀĆ ļ╣öņŚÉ ņØśĒĢ£ ļČäļ”¼ ĒÖłņØ┤ ļ¦īļōżņ¢┤ņ¦ä Ēøä ņŚ┤ĒīĮņ░ĮņŚÉ ņØśĒĢ┤ ļČäļ”¼ļÉ£ ņø©ņØ┤ĒŹ╝ņŚÉ ļ░£ņāØĒĢ£ ņ╣®ĒĢæ ņåÉņāüņØä ļ│┤ņŚ¼ņŻ╝ļŖö ņé¼ņ¦äņØ┤ļŗż. ņĀäņłĀĒĢ£ Ļ▓āņ▓śļ¤╝ ņØ┤ļ¤¼ĒĢ£ ņ╣®ĒĢæņØ┤ ļ░£ņāØĒĢĀ Ļ▓ĮņÜ░ ņø©ņØ┤ĒŹ╝ Ēæ£ļ®┤ņŚÉ ņןņ░®ļÉ£ ņĢĪĒŗ░ļĖī ļööļ░öņØ┤ņŖżņØś ņåÉņāüņ£╝ļĪ£ ņØ┤ņ¢┤ņ¦ł ņłś ņ׳ĻĖ░ ļĢīļ¼ĖņŚÉ ļööļ░öņØ┤ņŖż ņé¼ņØ┤ņŚÉ ņŖżĒü¼ļØ╝ņØ┤ļĖī ņ¦ĆņŚŁņØ┤ļØ╝ ļČłļ”¼ļŖö ņØ╝ņĀĢ ņŚ¼ņ£Ā Ļ│ĄĻ░äņØä ļ¦īļōżņ¢┤ ļŗżņØ┤ņŗ▒ņŚÉ ņØśĒĢ£ ļööļ░öņØ┤ņŖż ņåÉņāüņØä ņśłļ░®ĒĢśņŚ¼ņĢ╝ ĒĢ£ļŗż [5]. ņØ┤ļ¤¼ĒĢ£ ņŖżĒü¼ļØ╝ņØ┤ļĖī ņ¦ĆņŚŁņØś Ēü¼ĻĖ░Ļ░Ć Ēü┤ņłśļĪØ ņø©ņØ┤ĒŹ╝ ļŗ╣ ļööļ░öņØ┤ņŖżļź╝ ļ¦īļōż ņłś ņ׳ļŖö ņŚ¼ņ£Ā Ļ│ĄĻ░äņØ┤ ņżäņ¢┤ļōżĻĖ░ ļĢīļ¼ĖņŚÉ ņ╣®ĒĢæ ņåÉņāüņØä ņĄ£ņåīĒÖöĒĢśņŚ¼ ņŖżĒü¼ļØ╝ņØ┤ļĖī ņ¦ĆņŚŁņØś ļ®┤ņĀüņØä ņĄ£ņåīĒÖöĒĢśļŖö Ļ▓āņØ┤ ļ░śļÅäņ▓┤ ņĀ£ĒÆłņØś ņāØņé░ņä▒ņØä ĻĘ╣ļīĆĒÖöņŗ£ĒéżļŖö ņ▓®Ļ▓ĮņØ┤ļŗż. ļ│Ė ņŚ░ĻĄ¼ņŚÉņä£ ļĀłņØ┤ņĀĆ ļŗżņØ┤ņŗ▒ Ļ│ĄņĀĢņØä ļÅäņ×ģĒĢ£ ņØ┤ņ£ĀļÅä Ļ░ÖņØĆ ļ¦źļØĮņ£╝ļĪ£ ņäżļ¬ģļÉĀ ņłś ņ׳ļŗż.

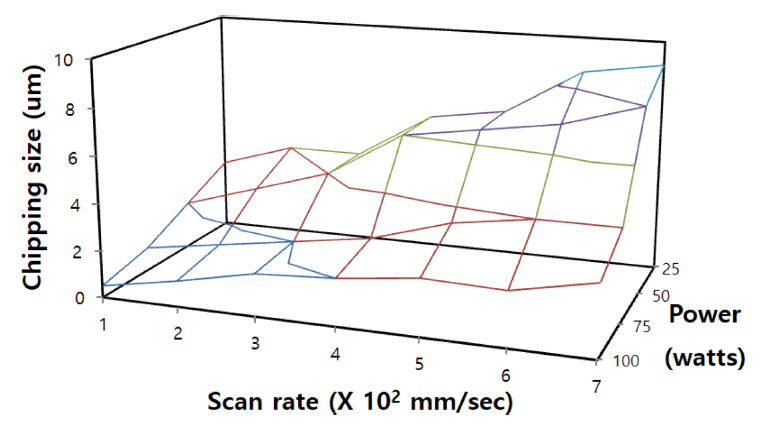

ļ│Ė ņŚ░ĻĄ¼ņŚÉņä£ļŖö ļĀłņØ┤ņĀĆ Ļ│ĄņĀĢ ļÅäņ×ģņ£╝ļĪ£ ņØĖĒĢ£ ļČäļ”¼ ĒÖłņØś ĒśĢņä▒ņŚÉ ņØśĒĢ┤ ņł£ņłśĒĢ£ ņåīņÜ░ņ×ē Ļ│ĄņĀĢ ļ│┤ļŗż ņ╣®ĒĢæ ņåÉņāü ļ▓öņ£äļŖö Ēü¼Ļ▓ī ņżäņØ╝ ņłś ņ׳ņ¦Ćļ¦ī ņø©ņØ┤ĒŹ╝ņØś ņĄ£ņóģ ļČäļ”¼Ļ│╝ņĀĢņŚÉņä£ ļ»ĖņäĖĒĢ£ ņ╣®ĒĢæ ņåÉņāüņØ┤ ņŚ¼ņĀäĒ׳ ļ░£ņāØĒĢĀ ņłś ņ׳ĻĖ░ ļĢīļ¼ĖņŚÉ ņØ┤ļ¤¼ĒĢ£ ļ»ĖņäĖ ņ╣®ĒĢæ ņåÉņāü ļ¦łņĀĆļÅä ņĄ£ņåīĒÖöĒĢĀ ņłś ņ׳ļŖö ļ░®ņĢłļōżņØ┤ ņŚ░ĻĄ¼ļÉśņŚłļŗż. ņØ┤ļź╝ ņ£äĒĢ┤ ņŚ¼ļ¤¼ ļĀłņØ┤ņĀĆ Ļ│ĄņĀĢņĪ░Ļ▒┤ļ│ä ņø©ņØ┤ĒŹ╝ Ēæ£ļ®┤ņŚÉ ĒśĢņä▒ļÉĀ ņłś ņ׳ļŖö ļČäļ”¼ ĒÖłļōżņØä ņ░©ļ│äĒÖöĒĢśņŚ¼ ņ╣®ĒĢæ ņåÉņāüņØä ņĄ£ņåīĒÖöĒĢĀ ņłś ņ׳ļŖö ļ░®ņĢłļōżņØä ņŚ░ĻĄ¼ĒĢśņśĆļŗż. ļĀłņØ┤ņĀĆ ļ╣öņØś ņĀäļĀź, ņŖżņ║ö ņåŹļÅä, ņŖżņ║ö Ēܤņłś ļō▒ņØä ļ│ĆņłśļĪ£ ĒĢśņŚ¼ ņø©ņØ┤ĒŹ╝ Ēæ£ļ®┤ņŚÉ ļĀłņØ┤ņĀĆ ļ╣öņŚÉ ņØśĒĢ┤ ĒśĢņä▒ļÉ£ ĻĘĖļŻ©ļĖīņØś ļ¬©ņ¢æĻ│╝ Ļ╣ŖņØ┤ ļō▒ņØä ļČäņäØĒĢśņśĆĻ│Ā, ĻĘĖ Ļ▓░Ļ│╝ļź╝ ĻĖ░ņ┤łļĪ£ ĒĢśņŚ¼ Ļ░üĻ░üņØś Ļ│ĄņĀĢņĪ░Ļ▒┤ļ│ä ņ╣®ĒĢæ ņåÉņāüņØś ļ▓öņ£äļź╝ ņĖĪņĀĢĒĢśņŚ¼ Ļ░Ćņן ĒÜ©ņ£©ņĀüņØĖ ļŗżņØ┤ņŗ▒ Ļ│ĄņĀĢ ļ░®ņĢłņŚÉ ļīĆĒĢ┤ ņŚ░ĻĄ¼ĒĢśņśĆļŗż. ĻĘĖļ”╝ 3ņØĆ ļĀłņØ┤ņĀĆ ļ╣öņØś ņĀäļĀźĻ│╝ ņŖżņ║ö ņåŹļÅäņØś ĒĢ©ņłśļĪ£ ņ╣®ĒĢæ ņåÉņāüņØś Ēü¼ĻĖ░ļź╝ ļéśĒāĆļéĖ ļÅäĒæ£ņØ┤ļŗż. ļ│Ė Ļ▓░Ļ│╝ņŚÉņä£ ļĀłņØ┤ņĀĆļ╣öņØś ņĀäļĀźņØ┤ ņ”ØĻ░ĆĒĢĀņłśļĪØ ņ╣®ĒĢæ ņåÉņāüņØ┤ ņżäņ¢┤ļō£ļŖö Ļ▓ĮĒ¢źņØ┤ ņ׳ļŗżļŖö Ļ▓āņØä ņĢī ņłś ņ׳ņŚłļŗż. ņØ┤ļŖö ļĀłņØ┤ņĀĆ ļ╣öņØś ņĀäļĀźņØ┤ Ēü┤ņłśļĪØ ņø©ņØ┤ĒŹ╝ Ēæ£ļ®┤ņŚÉ ĒśĢņä▒ļÉśļŖö ĻĘĖļŻ©ļĖīņØś Ļ╣ŖņØ┤Ļ░Ć Ļ╣Ŗņ¢┤ņ¦ĆĻĖ░ ļĢīļ¼Ėņ£╝ļĪ£ ņČ®ļČäĒ׳ ņśłĻ▓¼ļÉśņŚłļŹś Ļ▓░Ļ│╝ņØ┤ļŗż. ļśÉĒĢ£ ļĀłņØ┤ņĀĆ ļ╣öņØś ņŖżņ║öņåŹļÅäĻ░Ć ļŖÉļ”┤ņłśļĪØ ņ╣®ĒĢæ ņåÉņāüņØś Ēü¼ĻĖ░Ļ░Ć Ļ░ÉņåīĒĢ£ļŗżļŖö Ļ▓āņØä ĒÖĢņØĖĒĢĀ ņłś ņ׳ņŚłļŗż. ņØ┤ ļśÉĒĢ£ ņø©ņØ┤ĒŹ╝ Ēæ£ļ®┤ņŚÉ ļĀłņØ┤ņĀĆ ļ╣öņØś ļģĖņČ£ņŗ£Ļ░äņØ┤ ĻĖĖņ¢┤ ņ¦łņłśļĪØ ĻĘĖļŻ©ļĖīņØś Ļ╣ŖņØ┤Ļ░Ć Ļ╣Ŗņ¢┤ņ¦ĆĻĖ░ ļĢīļ¼Ėņ£╝ļĪ£ ļ│╝ ņłś ņ׳ļŗż. ļ│Ė ņŚ░ĻĄ¼ņŚÉņä£ļŖö ļĀłņØ┤ņĀĆ ņ¢┤ļĖīļĀłņØ┤ņģśņŚÉ ņØśĒĢ┤ ņø©ņØ┤ĒŹ╝ Ēæ£ļ®┤ņŚÉ ĒśĢņä▒ļÉśļŖö ĻĘĖļŻ©ļĖīņØś Ļ╣ŖņØ┤Ļ░Ć Ļ╣Ŗņ¢┤ņ¦ĆĻ│Ā ĻĘĖ Ļ▓░Ļ│╝ ņ╣®ĒĢæņåÉņāü ļ▓öņ£äĻ░Ć ņżäņ¢┤ļōĀļŗżļŖö ņé¼ņŗżņŚÉ ļīĆĒĢ£ ļ│┤ļŗż ļ¬ģĒÖĢĒĢ£ ĻĘ╝Ļ▒░ļź╝ ņ░ŠĻĖ░ ņ£äĒĢ┤ ļĀłņØ┤ņĀĆ ļ╣öņŚÉ ņØśĒĢ┤ ĒśĢņä▒ļÉ£ ĻĘĖļŻ©ļĖīņØś ļŗ©ļ®┤ņØä ņŻ╝ņé¼ņĀäņ×ÉĒśäļ»ĖĻ▓Įņ£╝ļĪ£ ļČäņäØĒĢśņśĆļŗż. ĻĘĖļ”╝ 4(a)ļŖö ļĀłņØ┤ņĀĆ ļ╣öņØś ņĀäļĀźņØ┤ 100WņØ┤Ļ│Ā, ņŖżņ║ö ņåŹļÅäĻ░Ć 700 mm/sec ņØ╝ļĢī ņø©ņØ┤ĒŹ╝ Ēæ£ļ®┤ņŚÉ ļ░£ņāØļÉ£ ĻĘĖļŻ©ļĖīņØś ļŗ©ļ®┤ņØä ļ│┤ņŚ¼ņŻ╝ļŖö ņŻ╝ņé¼ņĀäņ×ÉĒśäļ»ĖĻ▓Į ņé¼ņ¦äņØ┤ļ®░, ĻĘĖļ”╝ 4(b)ļŖö ļĀłņØ┤ņĀĆ ļ╣öņØś ņĀäļĀźņØ┤ 100 WņØ┤Ļ│Ā, ņŖżņ║ö ņåŹļÅäĻ░Ć 100 mm/sec ņØ╝ļĢī ņø©ņØ┤ĒŹ╝ Ēæ£ļ®┤ņŚÉ ļ░£ņāØļÉ£ ĻĘĖļŻ©ļĖīņØś ļŗ©ļ®┤ņØä ļ│┤ņŚ¼ņŻ╝ļŖö ņŻ╝ņé¼ņĀäņ×ÉĒśäļ»ĖĻ▓Į ņé¼ņ¦äņØ┤ļŗż. ĻĘĖļ”╝ 4ņŚÉņä£ ĒÖĢņØĖĒĢĀ ņłś ņ׳ļō»ņØ┤ ļĀłņØ┤ņĀĆ ļ╣öņØś ņĀäļĀźņØ┤ļéś ņŖżņ║öņåŹļÅäņŚÉ ļö░ļØ╝ ĻĘĖļŻ©ļĖīņØś Ļ╣ŖņØ┤Ļ░Ć 2ļ░░ ņØ┤ņāü ņ░©ņØ┤ļź╝ ļéśĒāĆļéĖļŗżļŖö Ļ▓āņØä ļ│┤ņŚ¼ņżĆļŗż. ņØ┤ļŖö ļĀłņØ┤ņĀĆ Ļ│ĄņĀĢņĪ░Ļ▒┤ņŚÉ ļö░ļØ╝ ĻĘĖļŻ©ļĖīņØś Ļ╣ŖņØ┤Ļ░Ć ņ░©ļ│äĒÖöļÉśņ¢┤ ņ╣®ĒĢæ ņåÉņāüņØś ļ▓öņ£äņŚÉ ņ¦üņĀæņĀüņØĖ ņśüĒ¢źņØä ļ»Ėņ╣Ā ņłś ņ׳ļŗżļŖö ļ¬ģĒÖĢĒĢ£ ĻĘ╝Ļ▒░ņ×äņØä ņĢī ņłś ņ׳ļŗż. ļŗżļ¦ī, ĻĘĖļ”╝ 4(b)ņŚÉņä£ ļ│╝ ņłś ņ׳ļō»ņØ┤ ļĀłņØ┤ņĀĆņØś ņŖżņ║öņåŹļÅäĻ░Ć ļŖÉļ”┤ Ļ▓ĮņÜ░ ĻĘĖļŻ©ļĖī ĒīüņØś Ļ│Īņ£©ļ░śĻ▓ĮļÅä ņ”ØĻ░ĆĒĢĀ ņłś ņ׳ļŗżļŖö ņé¼ņŗżļÅä ĒÖĢņØĖĒĢśņśĆļŗż. ļŹöļČłņ¢┤, ļĀłņØ┤ņĀĆ ļ╣öņØś ņŖżņ║öņåŹļÅäļź╝ ļŖ”ņČöļŖö Ļ▓āņØĆ ņ×Éņ╣½ ļööļ░öņØ┤ņŖżĻ░Ć Ļ│╝ļŗżĒĢ£ ņŚ┤ņŚÉļäłņ¦ĆņŚÉ ļģĖņČ£ļÉĀ ņłś ņ׳ņ¢┤ ļśÉ ļŗżļźĖ ņŗĀļó░ņä▒ ļ¼ĖņĀ£ļź╝ ļ░£ņāØņŗ£Ēé¼ ņłś ņ׳ļŗż. ļö░ļØ╝ņä£, ļ│Ė ņŚ░ĻĄ¼ņŚÉņä£ļŖö ļĀłņØ┤ņĀĆ ļ╣öņØś ņŖżņ║öņåŹļÅäļź╝ ņĀüņĀĢĒĢśĻ▓ī ņ£Āņ¦ĆĒĢśļ®┤ņä£ ņŖżņ║ö Ēܤņłśļź╝ ļ│ĆĒÖöņŗ£ņ╝£ ņ╣®ĒĢæņåÉņāüņØä ņżäņØ╝ ņłś ņ׳ļŖö ļ░®ņĢłņŚÉ ļīĆĒĢ┤ ņČöĻ░ĆņĀüņ£╝ļĪ£ ņŚ░ĻĄ¼ĒĢśņśĆļŗż.

ĻĘĖļ”╝ 5ļŖö ļĀłņØ┤ņĀĆ ļ╣öņØś ņĀäļĀźĻ│╝ ļĀłņØ┤ņĀĆ ļ╣öņØś ņŖżņ║öņåŹļÅäļź╝ 700 mm/secļĪ£ Ļ│ĀņĀĢĒĢ£ Ēøä ņŖżņ║ö Ēܤņłśļź╝ ļ│ĆĒÖöņŗ£ņ╝£ ļČäļ”¼ļÉ£ ņø©ņØ┤ĒŹ╝ņØś ņĄ£ļīĆ ņ╣®ĒĢæņåÉņāü Ēü¼ĻĖ░ļź╝ ļéśĒāĆļéĖ ļÅäĒæ£ņØ┤ļŗż. ļ│Ė Ļ▓░Ļ│╝ņŚÉņä£ ņĢī ņłś ņ׳ļō»ņØ┤ ļĀłņØ┤ņĀĆ ļ╣öņØś ņŖżņ║öĒܤņłśĻ░Ć ņ”ØĻ░ĆĒĢĀņłśļĪØ ņ╣®ĒĢæņåÉņāüļ▓öņ£äĻ░Ć ņżäņ¢┤ļōĀļŗżļŖö Ļ▓āņØä ĒÖĢņØĖĒĢĀ ņłś ņ׳ņŚłļŗż. ĒŖ╣ņØ┤ĒĢ£ ņĀÉņØĆ 100WņØś ņĀäļĀźņŚÉņä£ ļŗ©ņØ╝ ĒܤņłśņØś ņŖżņ║öļ│┤ļŗżļŖö 25WņØś ņĀäļĀźņŚÉņä£ 7ĒÜīņØś ņŖżņ║öņŚÉņä£ ņ╣®ĒĢæ ņåÉņāüņØś Ēü¼ĻĖ░Ļ░Ć ļŹöņÜ▒ ĻĖēĻ▓®Ē׳ ņżäņ¢┤ļōż ņłś ņ׳ļŗżļŖö Ļ▓āņØ┤ļŗż. ņØ┤ļ¤¼ĒĢ£ ņŗżĒŚśĻ▓░Ļ│╝ņŚÉ ļīĆĒĢ£ ņøÉņØĖļČäņäØņØä ņ£äĒĢ┤ ļé«ņØĆ ņĀäļĀźņ£╝ļĪ£ ļĀłņØ┤ņĀĆ ņŖżņ║öĒܤņłśļź╝ ļŖśļĀż ņ¦äĒ¢ēļÉ£ ņø©ņØ┤ĒŹ╝ņØś ĻĘĖļŻ©ļĖī ļŗ©ļ®┤ņØä scanning electron microscopeļĪ£ ļČäņäØĒĢśņśĆļŗż.

ĻĘĖļ”╝ 6ņØĆ 25WņØś ņĀäļĀźņŚÉņä£ 7ĒÜī ņŖżņ║öĒĢśņŚ¼ ņø©ņØ┤ĒŹ╝ Ēæ£ļ®┤ņŚÉ ļ░£ņāØļÉ£ ĻĘĖļŻ©ļĖīņØś ļŗ©ļ®┤ņØä ļ│┤ņŚ¼ņŻ╝ļŖö ņĀäņ×ÉĒśäļ»ĖĻ▓Į ņé¼ņ¦äņØ┤ļŗż. ĻĘĖļ”╝ 6ņŚÉņä£ ļ│╝ ņłś ņ׳ļō»ņØ┤ ļé«ņØĆ ņĀäļĀźņŚÉņä£ ņŚ¼ļ¤¼ļ▓ł ņŖżņ║öĒĢ£ ņŗ£ĒÄĖņØś Ļ▓ĮņÜ░Ļ░Ć ļåÆņØĆ ņĀäļĀźņŚÉņä£ ļŗ©ņØ╝ ņŖżņ║öĒĢ£ ņŗ£ĒÄĖ ļ│┤ļŗż ĻĘĖļŻ©ļĖīĒīü Ļ│Īņ£© ļ░śĻ▓ĮņØ┤ Ēø©ņö¼ ļŹö ņ×æņĢä ļģĖņ╣śĒÜ©Ļ│╝ļź╝ ļŹöņÜ▒ ĻĘ╣ļīĆĒÖöņŗ£Ēé¼ ņłś ņ׳ļŗżļŖö Ļ▓āņØä ĒÖĢņØĖĒĢĀ ņłś ņ׳ņŚłļŗż. ļ¼╝ļĪĀ ļĀłņØ┤ņĀĆ ļ╣öņØś ņŖżņ║öĒܤņłśĻ░Ć ņ”ØĻ░ĆĒĢśļŖö Ļ▓āņØĆ ļ░śļÅäņ▓┤ ņāØņé░ ņåŹļÅäļź╝ ļŖ”ņČöļŖö ļŗ©ņĀÉņØ┤ ņ׳ņ¦Ćļ¦ī, ĒĢ£ļ▓łņŚÉ ļ¦ÄņØĆ ņŚ┤ņŚÉļäłņ¦Ćļź╝ ņø©ņØ┤ĒŹ╝ņŚÉ Ļ░ĆĒĢśņ¦Ć ņĢŖĻ│Ā ļīĆņŗĀ ļĀłņØ┤ņĀĆņŚÉ ņØśĒĢ£ ņŚ┤ņØä ļ░®ņČ£ĒĢĀ ņłś ņ׳ļŖö ņŗ£Ļ░äņĀü ņŚ¼ņ£Āļź╝ Ļ░¢Ļ▓ī ļÉ£ļŗżļŖö ņĀÉņŚÉņä£ ņø©ņØ┤ĒŹ╝ņŚÉ ņןņ░®ļÉ£ ļööļ░öņØ┤ņŖżņØś ņŗĀļó░ņä▒ ĒÖĢļ│┤ņŚÉļŖö ļÅäņøĆņØ┤ ļÉĀ Ļ▓āņ£╝ļĪ£ ĒīÉļŗ©ļÉ£ļŗż. Ļ▓░ļĪĀņĀüņ£╝ļĪ£ ĻĘĖļ”╝ 6ņŚÉņä£ ļ│╝ ņłś ņ׳ļō»ņØ┤ ļé«ņØĆ ņĀäļĀźņŚÉņä£ ļ╣ĀļźĖ ņåŹļÅäņØś ļĀłņØ┤ņĀĆ ļ╣öņ£╝ļĪ£ 7ĒÜī ņŖżņ║öĒĢśņŚ¼ ĒśĢņä▒ļÉ£ ļČäļ”¼ ĒÖłņØĆ ļåÆņØĆ ļĀłņØ┤ņĀĆ ļ╣ö ņĀäļĀźņŚÉņä£ ļŖÉļ”░ ņŖżņ║ö ņåŹļÅäļĪ£ ļŗ©ņØ╝ ņŖżņ║öĒĢśņŚ¼ ĒśĢņä▒ļÉ£ ļČäļ”¼ ĒÖł ļ│┤ļŗż ĻĘĖļŻ©ļĖīņØś Ļ╣ŖņØ┤ļŖö Ļ╣Ŗņ¦Ć ņĢŖņ£╝ļéś ĻĘĖļŻ©ļĖī ĒīüņØś Ļ│Īņ£© ļ░śĻ▓ĮņØ┤ ņ×æņĢä ņāüļīĆņĀüņ£╝ļĪ£ ņø©ņØ┤ĒŹ╝ņØś ņĄ£ņóģ ļČäļ”¼Ļ│╝ņĀĢņŚÉņä£ ņ╣®ĒĢæ ņåÉņāüņØä ņĄ£ņåīĒÖöĒĢśļŖöļŹ░ ļÅäņøĆņØ┤ ļÉśļŖö Ļ▓āņ£╝ļĪ£ ĒÅēĻ░ĆļÉśņŚłļŗż.

ļĀłņØ┤ņĀĆ Ļ│ĄņĀĢ ņ░©ļ│äĒÖö ņ”ē, ĻĘĖļŻ©ļĖī ĒīüņØś Ļ│Īņ£© ļ░śĻ▓ĮņØ┤ ņ×æņØä Ļ▓ĮņÜ░ ļČäļ”¼ļÉ£ ņø©ņØ┤ĒŹ╝ņØś ņ╣®ĒĢæ ņåÉņāüņØ┤ ņżäņ¢┤ļō£ļŖö ņøÉņØĖņŚÉ ļīĆĒĢ£ ņóĆ ļŹö ņŗ¼ļÅä ņ׳ļŖö ņŚ░ĻĄ¼ļź╝ ņ£äĒĢ┤ ļČäļ”¼ļÉ£ ņø©ņØ┤ĒŹ╝ņØś Ēīīļŗ©ļ®┤ņŚÉ ļīĆĒĢ£ AFM(atomic force microscope) ļČäņäØņØ┤ ņČöĻ░ĆņĀüņ£╝ļĪ£ ņŗżņŗ£ļÉśņŚłļŗż. ĻĘĖļ”╝ 7(a)ļŖö ļĀłņØ┤ņĀĆņØś ņĀäļĀźņØ┤ 100WņØ┤Ļ│Ā ļŗ©ņØ╝ņŖżņ║öņØ┤ ņĀüņÜ®ļÉśņ¢┤ ļČäļ”¼ļÉ£ ņø©ņØ┤ĒŹ╝ņØś Ēīīļŗ©ļ®┤ņØä ļ│┤ņŚ¼ņŻ╝ļŖö atomic force microscope ņé¼ņ¦äņØ┤ļ®░, ĻĘĖļ”╝ 7(b)ļŖö ļĀłņØ┤ņĀĆņØś ņĀäļĀźņØ┤ 25 WņØ┤Ļ│Ā, ņŖżņ║ö ĒܤņłśĻ░Ć 7ĒÜīņØĖ ņĪ░Ļ▒┤ĒĢśņŚÉņä£ ļČäļ”¼ļÉ£ ņø©ņØ┤ĒŹ╝ņØś Ēīīļŗ©ļ®┤ņØä ļ│┤ņŚ¼ņŻ╝ļŖö atomic force microscope ņé¼ņ¦äņØ┤ļŗż. Atomic force microscope ļČäņäØ Ļ▓░Ļ│╝ ļåÆņØĆ ņĀäļĀźņØś ļĀłņØ┤ņĀĆ ļ╣öņØ┤ ĒĢ£ļ▓ł ņŖżņ║öĒĢśņŚ¼ ļČäļ”¼ļÉ£ ņø©ņØ┤ĒŹ╝ņØś Ēīīļŗ©ļ®┤ņØ┤ ļé«ņØĆ ņĀäļĀźņØś ļĀłņØ┤ņĀĆ ļ╣öņØ┤ 7ļ▓ł ņŖżņ║öĒĢśņŚ¼ ļČäļ”¼ļÉ£ ņø©ņØ┤ĒŹ╝ņØś Ēīīļŗ©ļ®┤ ļ│┤ļŗż Ēæ£ļ®┤ņØ┤ ļŹöņÜ▒ Ļ▒░ņ╣ĀļŗżļŖö Ļ▓āņØä ļ¬ģĒÖĢĒ׳ ļ│┤ņŚ¼ņŻ╝Ļ│Ā ņ׳ļŗż. ņØ┤ļ¤¼ĒĢ£ ļČäņäØņØĆ ĻĘĖļ”╝ 5ņŚÉņä£ ļ│┤ņŚ¼ņżĆ Ļ▓āņ▓śļ¤╝ ļé«ņØĆ ņĀäļĀźņŚÉņä£ ņŖżņ║ö ĒܤņłśĻ░Ć 7ĒÜī ņØ┤ņāüņØ╝ Ļ▓ĮņÜ░ ņ╣®ĒĢæ ņåÉņāüņØ┤ ņÖ£ ĻĖēĻ▓®Ē׳ ņżäņ¢┤ļō£ļŖöņ¦ĆņŚÉ ļīĆĒĢ£ ņØ┤ņ£Āļź╝ Ļ░äņĀæņĀüņ£╝ļĪ£ ņäżļ¬ģĒĢ┤ ņŻ╝Ļ│Ā ņ׳ļŗżĻ│Ā ļ│╝ ņłś ņ׳ļŗż. ņ”ē, ņŚŁĒĢÖņĀüņ£╝ļĪ£ ņäĖļØ╝ļ»╣ ĒŖ╣ņä▒ņØś ļČäļ”¼Ļ│╝ņĀĢņŚÉņä£ ĻĘĖļŻ©ļĖīņØ┤ Ļ╣ŖņØ┤Ļ░Ć ĻĘĖļŻ©ļĖī ĒīüņØś Ļ│ĪļźĀ ļ░śĻ▓Į ļ¬╗ņ¦Ć ņĢŖĻ▓ī ņżæņÜöĒĢśņ¦Ćļ¦ī ļ│Ė ņŚ░ĻĄ¼ņŚÉņä£ļŖö ĻĘĖļŻ©ļĖīņØś Ļ╣ŖņØ┤ ļ│┤ļŗżļŖö ĻĘĖļŻ©ļĖī ĒīüņØś Ļ│Īņ£© ļ░śĻ▓ĮņØ┤ Ēīīļŗ©ļ®┤ņŚÉ ļŹö Ēü░ ņśüĒ¢ź ļ»Ėņ╣Ā ņłś ņ׳ļŗżļŖö Ļ▓āņØä ļ│┤ņŚ¼ņŻ╝ļŖöļŹ░ ņØ┤Ļ▓āņØĆ ļ░śļÅäņ▓┤ ņĀ£ĒÆłņÜ® ņŗżļ”¼ņĮś ņø©ņØ┤ĒŹ╝Ļ░Ć ļŗ©Ļ▓░ņĀĢņØ┤ĻĖ░ ļĢīļ¼ĖņŚÉ Ļ░ĆļŖźĒĢ£ Ļ▓āņ£╝ļĪ£ ĒĢ┤ņäØļÉĀ ņłś ņ׳ļŗż. ļČĆņ¢ĖĒĢśļ®┤ ĻĘĖļŻ©ļĖī ĒīüņØś Ļ│Īņ£©ļ░śĻ▓ĮņØ┤ ņ×æņØä Ļ▓ĮņÜ░ ņø©ņØ┤ĒŹ╝ ļŗżņØ┤ņŗ▒ ļ®┤ņØä ļö░ļØ╝ {011} ļ▓ĮĻ░£ĒīīĻ┤┤ņØś Ļ░ĆļŖźņä▒ņØ┤ ĻĘĖļ¦īĒü╝ ņ╗żņ¦ĆĻĖ░ ļĢīļ¼ĖņŚÉ ļČäļ”¼Ļ│╝ņĀĢņŚÉņä£ņØś ņ╣®ĒĢæ ņåÉņāüņØ┤ ņĄ£ņåīĒÖöļÉĀ ņłś ņ׳ļŖö Ļ▓āņ£╝ļĪ£ ĒĢ┤ņäØļÉĀ ņłś ņ׳ļŗż [9,10]. ļ░śļ®┤, ĻĘĖļŻ©ļĖī Ļ╣ŖņØ┤Ļ░Ć Ļ╣ŖļŹöļØ╝ļÅä ĒīüņØś Ļ│Īņ£©ļ░śĻ▓ĮņØ┤ Ēü┤ Ļ▓ĮņÜ░ņŚÉļŖö ņø©ņØ┤ĒŹ╝ņØś ļŗżņØ┤ņŗ▒ ļ®┤ņØä ļö░ļØ╝ ļ░£ņāØĒĢśļŖö ņø©ņØ┤ĒŹ╝ ļČäļ”¼Ļ░Ć {011} ļ▓ĮĻ░£ļ®┤ņØś ņØ┤ņĀÉņØä ņČ®ļČäĒ׳ ņé┤ļ”¼ņ¦Ć ļ¬╗ĒĢśņŚ¼ ņ╣®ĒĢæ ņåÉņāüņØś ļ▓öņ£äļź╝ ņČ®ļČäĒ׳ ņżäņØ┤ņ¦Ć ļ¬╗ĒĢśļŖö Ļ▓āņ£╝ļĪ£ ĒĢ┤ņäØļÉĀ ņłś ņ׳ļŗż. Ļ▓░ĻĄŁ, ļ│Ė ņŚ░ĻĄ¼ņŚÉņä£ ņ╣®ĒĢæ ņåÉņāüņØś ļ▓öņ£äļŖö ļĀłņØ┤ņĀĆņŚÉ ņØśĒĢ┤ ĒśĢņä▒ļÉ£ ļČäļ”¼ ĒÖłņØ┤ ņø©ņØ┤ĒŹ╝ņØś ļ▓ĮĻ░£ĒīīĻ┤┤ņŚÉ ņ¢╝ļ¦łļéś ņ£ĀņÜ®ĒĢśĻ▓ī ņ×æņÜ®ĒĢśļŖÉļāÉņŚÉ ņØśĒĢ┤ Ļ▓░ņĀĢļÉśļŖö Ļ▓āņ£╝ļĪ£ ĒīÉļŗ©ļÉ£ļŗż.

ņŚŁĒĢÖņĀüņ£╝ļĪ£ ņø©ņØ┤ĒŹ╝ņØś ņŚ┤ĒīĮņ░Į Ļ│╝ņĀĢņŚÉņä£ ĻĘĖļŻ©ļĖī ĒīüņŚÉ ļ░£ņāØĒĢśļŖö ņØæļĀźņØĆ ņĢäļלņÖĆ Ļ░Öļŗż [11]. (ĻĘĖļ”╝ 1 ņ░ĖņĪ░)

ļŗ©, Žā1ņØĆ ņØĖņןņä▒ļČäņØś ĻĘĖļŻ©ļĖī ĒīüņŚÉ ņ×æņÜ®ĒĢśļŖö ņØĖņןņØæļĀź, RņØĆ ĻĘĖļŻ©ļĖī ĒīüņØś Ļ│ĪļźĀ ļ░śĻ▓Į ĻĘĖļ”¼Ļ│Ā nņØĆ ĻĖ░ĒĢśĒĢÖņĀü ņāüņłś

ņ£äņØś ņłśņŗØņŚÉņä£ ļīĆļČĆļČäņØś ņäĖļØ╝ļ»╣ ņ×¼ļŻīņØś Ļ▓ĮņÜ░ nņØĆ 1 ņØ┤ĒĢśņØś Ļ░ÆņØä Ļ░¢ĻĖ░ ļĢīļ¼ĖņŚÉ ņŚŁĒĢÖņĀüņ£╝ļĪ£ ņø©ņØ┤ĒŹ╝ņØś ņŚ┤ĒīĮņ░Į Ļ│╝ņĀĢņŚÉņä£ ĻĘĖļŻ©ļĖī ĒīüņŚÉ ļ░£ņāØĒĢśļŖö ņØĖņןņä▒ļČäņØś ņØæļĀźņØĆ Ļ│Īņ£©ļ░śĻ▓ĮņŚÉ ļīĆļŗ©Ē׳ ļ»╝Ļ░ÉĒĢ£ ĒÄĖņØĆ ņĢäļŗłļŗż. ĻĘĖļ¤¼ļéś, ņŻ╝ņ¢┤ņ¦ä ņØæļĀź ĒĢśņŚÉņä£ ļŗ©Ļ▓░ņĀĢ ņŗżļ”¼ņĮśņØś ĒīīĻ┤┤Ļ░ĢļÅäļŖö Ļ▓░ņĀĢļ░®Ē¢źņŚÉ ļö░ļØ╝ ņāüļŗ╣Ē׳ ļŗ¼ļØ╝ņ¦ł ņłś ņ׳ļŗż [5]. ĒāĆļŗ╣ĒĢ£ ņØ┤ņ£ĀļŖö Ļ▓░ņĀĢļ░®Ē¢źņŚÉ ļö░ļØ╝ ņŗżļ”¼ņĮś ņøÉņ×ÉņØś ņĀÉņ£Āļ░ĆļÅäĻ░Ć ļŗżļź┤ĻĖ░ ļĢīļ¼ĖņŚÉ ĻĘĀņŚ┤ņØś ņä▒ņןņŚÉ ĒĢäņÜöĒĢ£ Ēīīļŗ©ļ®┤ ņāØņä▒ ņŚÉļäłņ¦ĆĻ░Ć ņ░©ļ│äĒÖö ļÉĀ ņłś ņ׳ĻĖ░ ļĢīļ¼ĖņØ┤ļŗż [9,10]. ņśłļź╝ļōżņ¢┤, {011} Ļ▓░ņĀĢļ®┤ņØś Ļ▓ĮņÜ░ ņŗżļ”¼ņĮś ņøÉņ×ÉņØś ņĀÉņ£Āļ░ĆļÅäĻ░Ć 42% ņĀĢļÅäļĪ£ {001} Ļ▓░ņĀĢļ®┤ņØś ņøÉņ×É ņĀÉņ£Āļ░ĆļÅäņØĖ 29% ļ│┤ļŗż ņøöļō▒Ē׳ ļåÆņĢä ĻĘĀņŚ┤ņØś ņä▒ņןņØ┤ ļŹö ņē¼ņÜ┤ Ļ▓āņ£╝ļĪ£ ņĢīļĀżņĀĖ ņ׳ļŗż [5,9,10]. ļö░ļØ╝ņä£, ļ│Ė ņŚ░ĻĄ¼ņŚÉņä£ ĻĘĖļŻ©ļĖī ĒīüņŚÉ ļ░£ņāØĒĢśļŖö ņØæļĀźņØś ņĀłļīĆņĀüņØĖ Ēü¼ĻĖ░ ļ│┤ļŗżļŖö ņŻ╝ņ¢┤ņ¦ä ņØæļĀźņØ┤ {011} Ļ▓░ņĀĢļ®┤ņ£╝ļĪ£ņØś ĻĘĀņŚ┤ ņä▒ņןņŚÉ ņ¢╝ļ¦łļéś ĒÜ©Ļ│╝ņĀüņ£╝ļĪ£ ņ×æņÜ®ĒĢĀ ņłś ņ׳ļŖö ņ¦ĆĻ░Ć ļīĆļŗ©Ē׳ ņżæņÜöĒĢ£ ļ│ĆņłśĻ░Ć ļÉĀ ņłś ņ׳ļŗżļŖö ņČöļĪĀņØ┤ Ļ░ĆļŖźĒĢśļŗż.

ĻĘĖļ”╝ 8ņØĆ ņāüĻĖ░ņØś ņØ┤ļĪĀņĀü ļ░░Ļ▓ĮĻ│╝ ļČäņäØĻ▓░Ļ│╝ļź╝ ĻĘ╝Ļ▒░ļĪ£ ļĀłņØ┤ņĀĆņŚÉ ņØśĒĢ┤ ĒśĢņä▒ļÉ£ ĻĘĖļŻ©ļĖīņØś ņ£äņ╣ś ļ░Å ļŗ©Ļ▓░ņĀĢ ņŗżļ”¼ņĮś ņø©ņØ┤ĒŹ╝ņØś ļ▓ĮĻ░£ļ®┤ ļō▒ņØä ļÅäņŗØņĀüņ£╝ļĪ£ ļ│┤ņŚ¼ņŻ╝ļŖö ĻĘĖļ”╝ņØ┤ļŗż. ļ│Ė ĻĘĖļ”╝ņŚÉņä£ ņĢī ņłś ņ׳ļō»ņØ┤ ļĀłņØ┤ņĀĆ ļ╣öņŚÉ ņØśĒĢ┤ ļ░£ņāØļÉśļŖö ĻĘĖļŻ©ļĖī ĒīüņØś Ļ│ĪļźĀ ļ░śĻ▓ĮņØ┤ ņ×æņØäņłśļĪØ ļ▓ĮĻ░£ļ®┤ (011)ņØä ļö░ļØ╝ ņØĖņן ņØæļĀźņØś ņ¦æņżæļÅäĻ░Ć ĻĘ╣ļīĆĒÖöļÉĀ ņłś ņ׳ļŗżļŖö Ļ▓āņØä ņĢī ņłś ņ׳ļŗż. ĻĘĖ Ļ▓░Ļ│╝ ļ▓ĮĻ░£ĒīīĻ┤┤ņØś Ļ░ĆļŖźņä▒ņØ┤ ĻĘĖļ¦īĒü╝ ņ╗żņĀĖņä£ ņø©ņØ┤ĒŹ╝ ļČäļ”¼Ļ░Ć ļööļ░öņØ┤ņŖż Ēæ£ļ®┤ņŚÉ ņłśņ¦üĒĢ£ (011) Ļ▓░ņĀĢļ®┤ņŚÉ ņ¦æņżæļÉśņ¢┤ ņ╣®ĒĢæ ņåÉņāüļ▓öņ£äĻ░Ć ņĄ£ņåīĒÖö ļÉĀ ņłś ņ׳ļŗżļŖö Ļ▓āņØä ļÅäņŗØņĀüņ£╝ļĪ£ ļ│┤ņŚ¼ņżĆļŗż.

4. Ļ▓░ ļĪĀ

ļ│Ė ņŚ░ĻĄ¼ņŚÉņä£ļŖö ņĀüņĀłĒĢ£ ļĀłņØ┤ņĀĆ Ļ│ĄņĀĢņŚÉ ņØśĒĢ┤ ņø©ņØ┤ĒŹ╝ ņŖżĒü¼ļØ╝ņØ┤ļĖī ņ¦ĆņŚŁ ņżæņĢÖņäĀņØä ļö░ļØ╝ ĒśĢņä▒ļÉ£ ļČäļ”¼ ĒÖłņØĆ ĻĘĖ ļ¬©ņ¢æĻ│╝ Ļ╣ŖņØ┤ņŚÉ ļö░ļØ╝ ņø©ņØ┤ĒŹ╝ņØś ņĄ£ņóģ ļČäļ”¼Ļ│╝ņĀĢņŚÉņä£ ļ░£ņāØĒĢśļŖö ņ╣®ĒĢæ ņåÉņāüņŚÉ ņāüļŗ╣Ē׳ Ēü░ ņśüĒ¢źņØä ņżä ņłś ņ׳ļŗżļŖö Ļ▓āņØä ņ×ģņ”ØĒĢśņśĆļŗż. ĒŖ╣ļ│äĒ׳, ļĀłņØ┤ņĀĆ ņĀäļĀźņØ┤ 25WņØ┤Ļ│Ā, ņŖżņ║ö ĒܤņłśĻ░Ć 7ĒÜīņØĖ Ļ│ĄņĀĢņŚÉ ņØśĒĢ┤ ĒśĢņä▒ļÉ£ ļČäļ”¼ ĒÖłņØś Ļ▓ĮņÜ░ ļĀłņØ┤ņĀĆ ļ╣öņØś ņĀäļĀźņØ┤ 100 WņØ┤Ļ│Ā, ļŗ©ņØ╝ ņŖżņ║öņŚÉ ņØśĒĢ┤ ĒśĢņä▒ļÉ£ ļČäļ”¼ ĒÖł ļ│┤ļŗż ĒÖłņØś Ļ╣ŖņØ┤ļŖö Ļ╣Ŗņ¦Ć ņĢŖĒä░ļØ╝ļÅä ņ╣®ĒĢæ ņåÉņāüņØä ņżäņØ┤ļŖöļŹ░ ļŹö ĒÜ©Ļ│╝ņĀüņØ┤ļØ╝ļŖö Ļ▓āņØä ņĢī ņłś ņ׳ņŚłļŗż. SEMĻ│╝ AFM ņé¼ņ¦ä ļČäņäØņØä ĒåĄĒĢ┤ ļé«ņØĆ ņĀäļĀźņŚÉņä£ ņŚ¼ļ¤¼ ļ▓łņØś ņŖżņ║öņŚÉ ņØśĒĢ┤ ĒśĢņä▒ļÉ£ ļČäļ”¼ ĒÖłņØś Ļ▓ĮņÜ░ ĻĘĖļŻ©ļĖī ĒīüņØś Ļ│ĪļźĀ ļ░śĻ▓ĮņØ┤ ņāüļīĆņĀüņ£╝ļĪ£ ņ×æņĢä ņø©ņØ┤ĒŹ╝ņØś {011} Ļ▓░ņĀĢļ®┤ņØä ļö░ļØ╝ ļ▓ĮĻ░£ĒīīĻ┤┤ļź╝ ņ£ĀļÅäĒĢśļŖöļŹ░ ļŹöņÜ▒ ņ£Āļ”¼ĒĢĀ ņłś ņ׳ļŗżļŖö Ļ▓āņØä Ļ▓Ćņ”ØĒĢĀ ņłś ņ׳ņŚłļŗż. Ļ▓░ĻĄŁ, ņ╣®ĒĢæ ņåÉņāü ņĄ£ņåīĒÖöņØś ĒĢ£ņĀĢļÉ£ ļ¬®ņĀüĒĢśņŚÉņä£ļŖö ļĀłņØ┤ņĀĆ Ļ│ĄņĀĢņŚÉ ņØśĒĢ£ ļČäļ”¼ ĒÖłņØś ļÅäņ×ģņØĆ ĒÖłņØś Ļ╣ŖņØ┤ ļ│┤ļŗżļŖö ĒÖłņØś Ēīü ļ¬©ņ¢æņØ┤ ļŹö ņżæņÜöĒĢśļ®░, ņØ┤ļŖö ļŗ©Ļ▓░ņĀĢ ņø©ņØ┤ĒŹ╝ņØś ļ▓ĮĻ░£ĒīīĻ┤┤ņØś ĒŖ╣ņä▒ ļĢīļ¼ĖņØĖ Ļ▓āņ×äņØä ņ”Øļ¬ģĒĢśņśĆļŗż. ļ│Ė ņŚ░ĻĄ¼ Ļ▓░Ļ│╝ļŖö ļ░śļÅäņ▓┤ ņø©ņØ┤ĒŹ╝ņØś ļŗżņØ┤ņŗ▒ Ļ│╝ņĀĢņŚÉņä£ ļ░£ņāØĒĢśļŖö ļČłļ¤ēļźĀ Ļ░ÉņåīņÖĆ Ļ░£ļ│ä ļööļ░öņØ┤ņŖżņØś ĒÆłņ¦ł Ē¢źņāüņŚÉ ĻĖ░ņŚ¼ĒĢĀ ņłś ņ׳ņØä Ļ▓āņ£╝ļĪ£ ĻĖ░ļīĆļÉ£ļŗż.